max_ii_cpld_sdram_tft_driver

This project no longer cont’d update as read back and write functions are completed.

Please provide pull requests to cont’d this project if any serious issues.

MAX II Altera’s CPLD TFT driver design with SDRAM and 8080 user interface supported.

The TFT model that is using in this design is AT070N92/94.

This controller support 8 display frames, which utilize the internal SDRAM 4 Banks (2 bits) and MSb of the Row address.

Please feel free to pull requests, update, and improve the design.

A micro example, the STM32F103 demonstartes how to control the CPLD-TFT driver (8080 mode).

Have fun~ =]

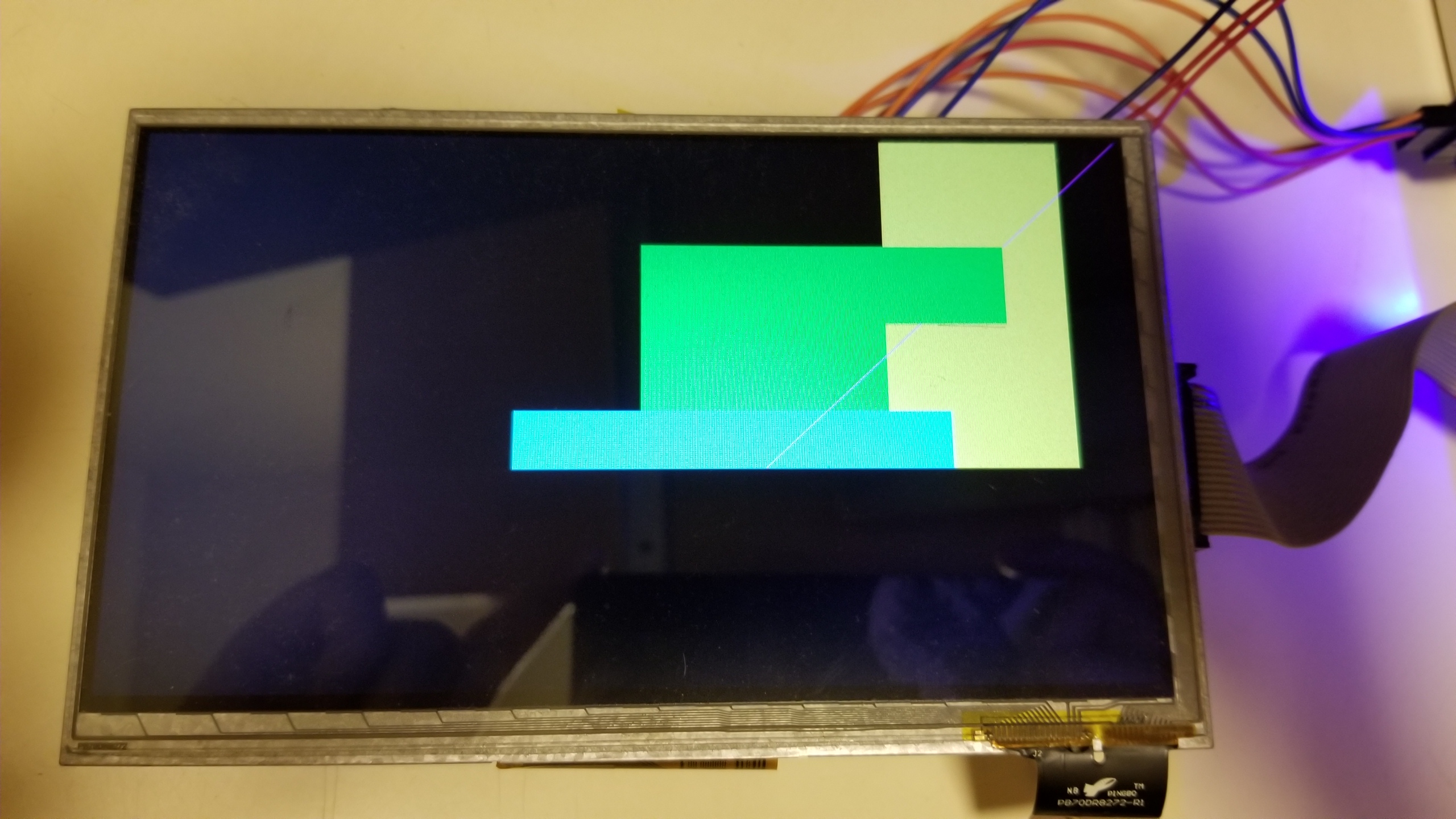

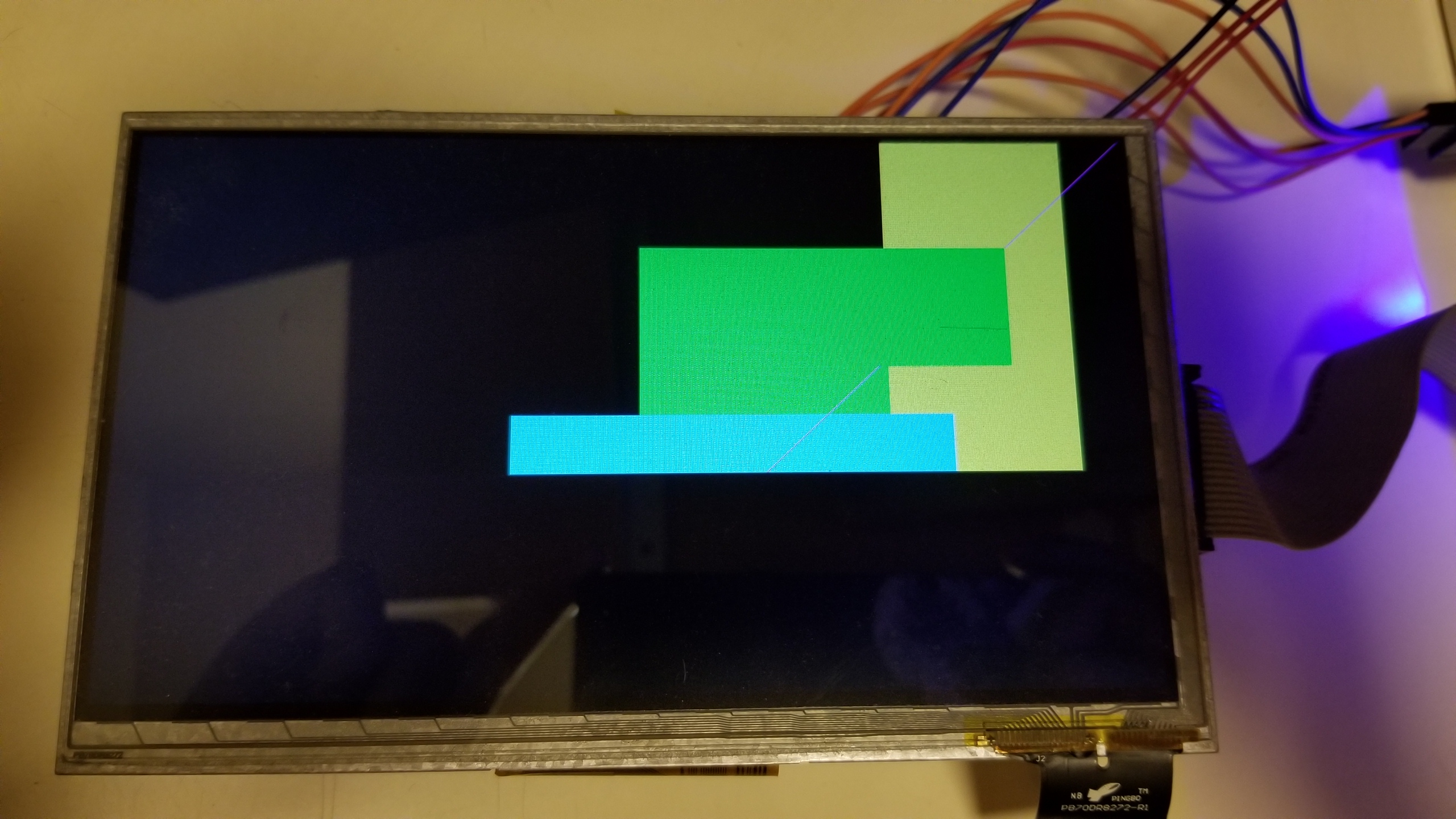

Here are the images of the TFT with the CPLD-SDRAM driver board:

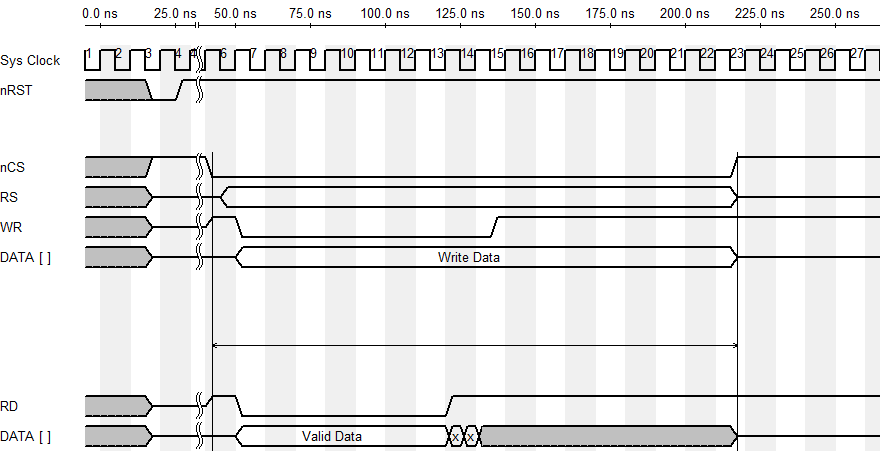

Timing:

Demo videos are embedded here:

Some demo images: